# Flexible Nanoscale High-Performance FinFETs

Galo A. Torres Sevilla,<sup>†</sup> Mohamed T. Ghoneim,<sup>†</sup> Hossain Fahad,<sup>†</sup> Jhonathan P. Rojas, Aftab M. Hussain, and Muhammad Mustafa Hussain<sup>\*</sup>

Integrated Nanotechnology Lab, King Abdullah University of Science and Technology, Thuwal, Makkah 23955-6900, Saudi Arabia. <sup>†</sup>Equally contributing authors.

**ABSTRACT** With the emergence of the Internet of Things (IoT), flexible high-performance nanoscale electronics are more desired. At the moment, FinFET is the most advanced transistor architecture used in the state-of-the-art microprocessors. Therefore, we show a soft-etch based substrate thinning process to transform silicon-on-insulator (SOI) based nanoscale FinFET into flexible FinFET and then conduct comprehensive electrical characterization under various bending conditions to understand its electrical performance. Our study shows that back-etch based substrate thinning process is gentler than traditional abrasive back-grinding process; it can attain ultraflexibility and the electrical characteristics of the flexible nanoscale FinFET show no performance degradation compared to its rigid bulk counterpart indicating its readiness to be used for flexible high-performance electronics.

#### **KEYWORDS:** flexible silicon · FinFETs · high-performance flexible electronics

ince the first introduction of the microprocessor in the early 1970s, silicon electronics have become an essential part of our daily life. Its unparalleled performance and cost-yield advantage makes silicon the most highly used material in today's digital world. With more than 90% of electronics based on silicon micro- and nanofabrication processes, silicon has become indispensable for our technologycentered lives. However, advances in ultramobile computation and implantable and wearable electronics are still hindered by silicon's brittleness and its inherited lack of flexibility. For this reason, in recent years, many different approaches to make flexible electronics have been introduced using polymer-based substrates.<sup>1-4</sup> Although polymer based electronics have shown exciting progress in displays and sensors,<sup>5</sup> their thermal instability and inherent low carrier mobility<sup>6</sup> hinder their potential for high performance and low stand-by power electronics used in today's ultramobile computation and communication devices. As a different approach, extremely high mobilities  $(10^3 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1})$  have been demonstrated with 2D single walled carbon nanotubes and graphene. However, the difficulty of integrating them with commonly known fabrication

techniques and their low integration density impede their potential to become candidates for future high performance electronics. Also, graphene's nearly zero bandgap property and doping difficulties makes it an undesired material for logic electronics due to the lack of distinguishable on/off behavior.<sup>7,8</sup> However, graphene's potential for radio frequency (RF) applications has already been demonstrated with promising results.9 To address all previous concerns, recently, many different transfer techniques have been demonstrated to combine the outstanding flexibility of polymer based substrates with the excellent electrical properties of silicon.<sup>10–18</sup> Transfer techniques are based on the creation of silicon nanoribbons from unorthodox (111) or expensive silicon-oninsulator substrate and then transferring them to a polymer based carrier substrate where the device is fabricated and tested. This approach shows promising results and advances in the area of unusual electronics. But still there is substantial area of improvement between transfer techniques and industry standard complementary metal oxide semiconductor (CMOS) processes. Ultra-large-scale-integration (ULSI) densities can only be achieved with today's most advanced lithographic techniques which

\* Address correspondence to Muhammadmustafa.hussain@kaust.edu.sa.

Received for review July 27, 2014 and accepted September 3, 2014.

Published online September 03, 2014 10.1021/nn5041608

© 2014 American Chemical Society

9850

involve critical alignment of different layers, making plastics an undesired substrate due to their nonuniformity. Also, etching and deposition techniques usually consist of using complex chemistry to remove undesired material from the substrate and in the case of plastic substrates, polymer cross contamination with the channel and gate stack is still an issue to be solved. On the other hand, alternate approaches to reduce silicon thickness have been recently developed using fracture of single crystalline substrates (spalling) at different depths in order to obtain thin flexible film.<sup>19,20</sup> However, the use of costly substrates like ET/UTSOI (compared to regular SOI that we have used), processes like high energy ion implantation, inherited limited bendability (nickel thin film has inherent high residual stress therefore bending is limited compared to our bending radius of <0.5 mm; additionally, global presence of highly stressful film potentially increases the risk of breaking the spalled substrate) and film opaqueness are some of the factors that limit their potential for high performance applications. One more technique has been developed which makes use of a double layer of monocrystalline silicon, while the first layer is kept intact for device fabrication, the bottom layer is anodic etched to introduce porosity allowing the top layer to be easily peeled off with stamp-transfer techniques.<sup>21,22</sup> Although highly complex circuits have been achieved with this method, the complexity of the process makes it difficult to integrate with known silicon microfabrication techniques. Also, the high processing costs associated with processes such as silicon epitaxy as well as limited flexibility in the resulting film hinder its potential for low-cost/ high-yield applications. Finally, commercially available thin silicon films have been introduced to overcome all previous problems. However, the higher cost in handling difficulties, fragility and processing complications make them undesired substrates for commonly known fabrication methods.

To eliminate all previous concerns, in recent years we have demonstrated a different method to transform conventional electronics into flexible ones without compromising cost, yield, performance and efficiency.<sup>23–27</sup> Since the process creates deterministic network of trenches/holes, we followed a back-etch process from the back-side of the substrate to eliminate any holes/trenches in the peeled-off (thinned down) silicon fabric. In this work we demonstrate the world's most advanced transistor architecture (FinFET) and material set (high- $\kappa$ /metal-gate) on a flexible monocrystalline silicon-based substrate. In addition to the advanced architecture and material set, we show a process to reduce silicon thickness in an easy and repeatable way in order to obtain high performance devices without comprising silicon's cost/yield advantage. The back etch process is softer than traditional back grinding, which is abrasive in nature and can thin

down a substrate to a limited thickness of 50  $\mu$ m only. Additionally, the objective of our study is to acquire a comprehensive understanding of the electrical characteristics of a flexible nanoscale FinFET; therefore, absence of hole/trenches in the flexible substrate offers a more holistic perspective on the device operation. The fabricated devices show extremely high performance and reduced short channel effects due to the increased electrostatic control achieved with dual-gate FinFETs. From all the perspectives, we envision this process and fabrication technique as a step forward toward very large scale integration of complex and high-performance circuits on flexible substrates.

# **FABRICATION**

The FinFETs fabrication process started with 8 in. SOI monitor grade wafers using state of the art gate first flow. First, the Fins were patterned using deep ultraviolet light (DUV) and resist trimming to obtain 20 nm features. Then, the top silicon layer was etched using anisotropic reactive ion etching (RIE). Next, we formed the gate stack with 10–20 nm of titanium nitride (TiN) as metal gate and 2-4 nm of hafnium dioxide (HfO<sub>2</sub>) as dielectric. Then, the gate is patterned to obtain different gate lengths (250 nm to 10  $\mu$ m). Source and drain were formed using ion implantation followed by NiSi to form ohmnic contact between the test pads and the gate, source and drain regions. Finally, activation anneal is performed on the fabricated wafers at 1000 °C for 10 s followed by forming gas anneal (FGA-N<sub>2</sub>/H<sub>2</sub> at 420 °C). Figure 1 shows the process to transform the fabricated devices into flexible ones. To process each die separately, the fabricated wafers were diced into 2.5 cm  $\times$  3 cm pieces (Figure 1a). At this point, each die is spin-coated with thick photoresist (PR, 7  $\mu$ m) to protect the on chip devices from the following thinning processes (Figure 1b). Then, the dies are turned upside-down and the back of the substrate is etched using anisotropic etching to reduce its thickness and achieve the required flexibility (Figure 1c). The backetching process is divided into 4 different steps to make sure that the required thickness is achieved without under or overetching. The first step reduces the thickness of the substrate from 800 to 200  $\mu$ m  $(\pm 30 \ \mu m)$  in a single etch step. Then, following the same methodology and changing the etching time, the substrate is etched 50  $\mu$ m in each step until the required 50  $\mu$ m in thickness is achieved (±10  $\mu$ m). The etch process is carried out at a temperature of -20 °C (Etch step, 7 s, 1300 W<sub>ICP</sub>, 30 W<sub>RF</sub>, 35 mTorr, 5 sccm C<sub>4</sub>F<sub>8</sub>, 120 sccm SF<sub>6</sub>; deposition step, 5 s, 1300  $W_{ICP}$ , 5  $W_{RF}$ , 35 mTorr, 100 sccm C<sub>4</sub>F<sub>8</sub>, 5 sccm SF<sub>6</sub>). It is important to note that between each etching step, a control thickness measurement of the substrate is performed in order to prevent over etching and damage of the onchip devices. All the measurements were done using two different profiling systems in order to confirm the

JAI

Figure 1. Fabrication process flow: (a) fabricated FinFET devices on standard 90 nm SOI with 150 nm BOX; (b) PR coating for chip-protection during back etch process; (c) FinFET die etched back using back grinding technique; (d) FinFET devices on flexible silicon substrate (50  $\mu$ m thick); and (e) PR removal and final device testing.

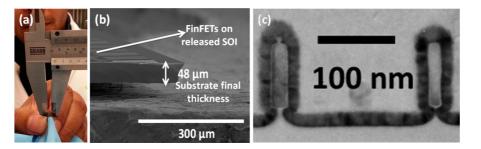

Figure 2. (a) A flexible silicon fabric with FinFETs wrapped around a blue plastic support measured at 0.5 mm bending radius; (b) SEM of flexible FinFET and (c) TEM of fabricated fins.

thickness of the substrate. The first system is a contactbased profiler DETAK-8, which makes use of microtip to measure the step size between two surfaces. The second system consists of an optical ZYGO profiler, which makes use of reflected light in order to measure the step size between two different surfaces. According to the readings, the difference between the measurements is less than  $\pm 5 \,\mu$ m. At this point, due to the reduced thickness of the substrate, the devices can be bent to a minimum-bending radius of 1.5 cm. Finally, the protecting PR is removed from the top of the substrate (Figure 1e) and the devices are tested at different bending conditions (compressive and tensile). Figure 2a shows the fabricated and processed FinFETs at 0.5 mm bending radius. To confirm the final thickness of the substrate, scanning electron microscopic (SEM) imaging of the sample was performed (Figure 2b). Finally, Figure 2c shows the resulting transmission electron microscopic (TEM) imaging of the patterned Fins on standard SOI wafer. For electrical characterization, we found P-MOS ( $L_g$  = 250 nm) and N-MOS ( $L_g$  = 1  $\mu$ m) has highest yield (out of nearly 200 devices yield rate was close to 75%).

## RESULTS

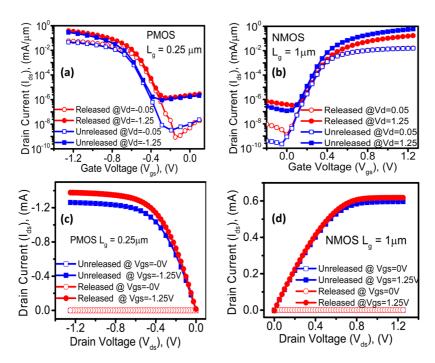

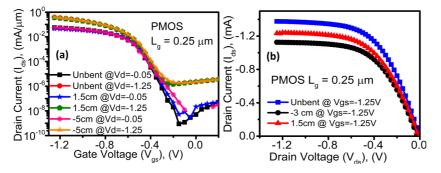

To study the behavior of the fabricated FinFETs, I-V characteristics were obtained in linear and saturation regions. The saturation currents at  $V_{GS} = \pm 1.25$  V and  $V_{DD} = \pm 1.25$  V for released P-MOS ( $L_g = 250$  nm) and N-MOS ( $L_g = 1 \mu$ m) FinFETs are 383 and 83  $\mu$ A/ $\mu$ m, respectively (Figure 3a,b). Figure 3c,d depicts the output characteristics of flexible N- and P-MOS devices. We focused our study on P-MOS (shorter  $L_g$ ) to comprehend a full analysis at different bending radii and stress direction (compressive and tensile). Figure 4a,b shows the transfer and output characteristics of released P-MOS at different bending radii.

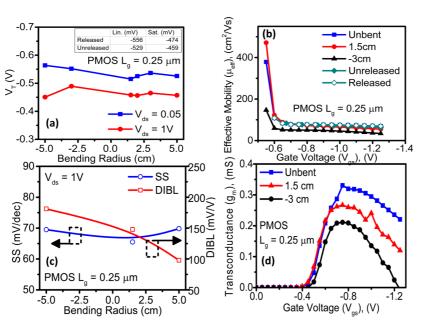

The electrical characterization started by extracting the threshold voltage of the devices ( $V_t$ ) from the  $I_D-V_G$  curve using linear extrapolation method.<sup>28</sup> With the  $I_D-V_G$  curves, the threshold voltage can be determined by

$$V_{\rm t} = V_{\rm GS_0} - \frac{V_{\rm DS}}{2}$$

(1)

where  $V_{GS0}$  is the intercepting point between the linear extrapolation at maximum slope of the  $I_D - V_G$  curve

VOL.8 • NO.10 • 9850-9856 • 2014

Figure 3. Unreleased and released transfer characteristics: (a) PMOS FinFET transfer curves ( $L_g = 250 \text{ nm}$ ,  $W = 3.6 \mu \text{m}$ ); (b) NMOS FinFET ( $L_g = 1 \mu m$ ,  $W = 3.6 \mu m$ ). Unreleased and released output characteristics: (c) PMOS FinFET transfer curves ( $L_g = 250 \text{ nm}$ ,  $W = 3.6 \mu m$ ) and (d) NMOS FinFET ( $L_g = 1 \mu m$ ,  $W = 3.6 \mu m$ ).

Figure 4. Unbent and bent (a) transfer and (b) output characteristics in flexible PMOS FinFETs ( $L_g = 250$  nm,  $W = 3.6 \mu$ m).

with the gate voltage axis. With eq 1, the obtained threshold voltage is -0.556 V in the linear region and -0.474 V in saturation (Figure 5a). To continue with the device characterization, mobility was extracted and calculated at low drain voltages by

$$\mu_{\rm eff} = \frac{L}{W} \frac{g_{\rm d}}{C_{\rm ox}(V_{\rm GS} - V_{\rm t})} \tag{2}$$

where *L* and *W* are the channel length and width of the transistor,  $V_{GS}$  and  $V_t$  are the gate to source voltage and threshold voltage, respectively,  $C_{ox}$  is the gate dielectric capacitance, and  $g_d$  is the drain conductance, which can be determined by

$$g_{\rm d} = \frac{\delta I_{\rm Deff}}{\delta V_{\rm DS}} \bigg| V_{\rm GS} = {\rm constant}$$

(3)

where  $I_{\text{Deff}}$  is the effective drain current and  $V_{\text{DS}}$  is the drain to source voltage.  $I_{\text{Deff}}$  is calculated when extremely scaled dielectric thickness is used in the transistor

fabrication causing gate leakage to oppose drain current and hence reducing the calculated mobility value. *I*<sub>Deff</sub> is calculated by

$$I_{\text{Deff}} = I_{\text{D}} + \frac{I_{\text{G}}}{2} \tag{4}$$

where  $I_D$  is the drain current and  $I_G$  is the gate current. With eqs 2, 3, and 4, the calculated peak effective mobility was found to be  $10^2 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  (Figure 5b). To continue the device characterization, the subthreshold swing was obtained from the  $I_D - V_G$  curve for released (63 mV/dec) and bent P-MOS (Figure 5c). Also, DIBL was extracted for P-MOS devices obtaining 68 mV/V in the case of released sample. Figure 5c also depicts the change in DIBL due to the induced stress during bending of the sample. The obtained value for  $I_{on}/I_{off}$  ratio in the case of released P-MOS devices is 5 decades and is kept almost unchanged at different bending radii (not shown). The obtained peak transconductance ( $g_m$ ) of the device was found to be 0.33 mS

VOL.8 • NO.10 • 9850-9856 • 2014 A

agnanc www.acsnano.org

Figure 5. (a) Threshold-voltage ( $V_t$ ) vs bending radii in flexible PMOS FinFETs ( $L_g = 250$  nm,  $W = 3.6 \,\mu$ m); (b) mobility variation due to bending; (c) subthreshold swing and DIBL vs bending radii and (d) bending effect on transconductance.

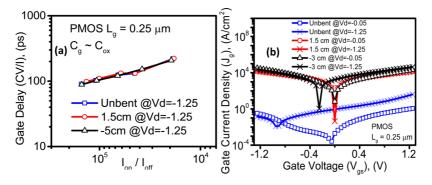

Figure 6. Effects of bending radii on (a) gate-delay and (b) leakage current density.

(Figure 5d). Also, the intrinsic gate delay was extracted using moving  $V_{\rm DD}$  method and is shown in Figure 6a depicting no significant changes at different bending conditions. Finally, the gate leakage  $J_{\rm G}$  was obtained to be 0.9 A/cm<sup>2</sup> in the case of released P-MOS devices. Figure 6b shows the obtained results for the gate leakage extraction at different bending radii.

For the first time, we also characterize the performance at different applied stress while bending the samples at different bending radii with a minimum compressive radius of 3 cm (bent downward) and a minimum tensile radius of 1.5 cm (bent upward). The maximum change in saturation current is 7.6% for PMOS at bending radius of 1.5 cm (0.17% tensile nominal strain). The maximum change SS is 10.3% for PMOS at a bending radius of 5 cm (0.05% tensile nominal strain). The maximum change in DIBL is 3.8 times for PMOS at bending radius of -5 cm (0.05% compressive nominal strain). The maximum change in  $J_{\rm G}$  is  $\sim$ 2 orders of magnitude for PMOS at a bending radius of -3 cm (0.08% compressive nominal strain). The maximum change in  $J_{\rm G}$  is -3 cm (0.08% compressive nominal strain).

SEVILLA ET AL.

saturation mode, at 1.5 cm, and -5 cm bending radius, respectively. The maximum change in peak  $g_m$  is 36.4% for PMOS at a bending radius of -3 cm. The maximum change in peak mobility is 29.6% for PMOS at a bending radius of 1.5 cm and  $V_{GS}$  of 0.625 V. The maximum change in  $I_{on}/I_{off}$  ratio is 15.9% for PMOS at a bending radius of 5 cm. Table 1 shows a comparison of the past reports and this work. Finally, the obtained results concur with previously reported studies, which show that saturation current is normally reduced when stress is applied in the longitudinal direction of the transistor's channel.<sup>29</sup>

#### DISCUSSION

In this work, we have demonstrated a CMOS compatible method to transform state of the art rigid silicon-on-insulator (SOI) based FinFET devices into flexible ones without comprising performance, integration density and cost/yield advantage of silicon microfabrication processes. Our method has the advantage of allowing complete fabrication of devices prior to release, allowing us to keep standard processes ARTICL

VOL.8 • NO.10 • 9850-9856 • 2014

ARTICLE

### TABLE 1. Comparison for Different Fabrication Methods of Flexible MOS Transistors

| group                                    | IBM (flex) <sup>30</sup> | Intel (rigid) <sup>31</sup> | this work (flex)   | Rogers (flex) <sup>32</sup> | Banerjee (flex) <sup>33</sup> |

|------------------------------------------|--------------------------|-----------------------------|--------------------|-----------------------------|-------------------------------|

| Arch.                                    | Planar                   | Tri-gate Fin                | Double-gate Fin    | Planar                      | Planar                        |

| L <sub>a</sub> (nm)                      | 40                       | 40                          | 1000(N)/250(P)     | 20000                       | 150                           |

| $\tilde{I_{on}}$ (mA/ $\mu$ m)           | 0.8(N)/ 0.5(P)           | 1.4(N)/1.1(P)               | 0.083(N)/ 0.383(P) | 0.00625(N)                  | 0.15(P)                       |

| $I_{\rm off}$ (nA/ $\mu$ m)              | 5                        | 100                         | 2.2                | 0.025                       | 1                             |

| I <sub>on</sub> /I <sub>off</sub>        | 10 <sup>5</sup>          | 10 <sup>4</sup>             | 10 <sup>5</sup>    | 10 <sup>5</sup>             | 10 <sup>6</sup>               |

| SS (mV/dec)                              | -                        | 90                          | 150(N)/63(P)       | 190                         | 72(N)/81(P)                   |

| V <sub>t</sub> (V)                       | 0.25                     | -                           | 0.36(N)/-0.556(P)  | -0.72                       | -                             |

| $\mu_{\rm eff}$ (cm <sup>2</sup> /(V s)) | -                        | 400(N)/ 200(P)              | 102(P)             | 375                         | 252(N)/51(P)                  |

without introducing any constraint in design and commonly know deposition, etching and lithography methods. Also, since the devices are completely silicon based and transfer to polymer substrates is not required, thermal budget constraints are kept intact when compared to industry standard processes. Our process then sets a major step toward true integration of state of the art ultramobile flexible ICs. The advantage offered by the superior electrical characteristic of inorganic substrates is here demonstrated that may be combined with standard industry processes to produce flexible devices. Also, the maturity of silicon microfabrication techniques makes the transformation of silicon semiconductor from rigid and brittle substrates to flexible ones the most logical step toward very large integration of flexible high performance electronics. We have also demonstrated that with the use of simple etching techniques and without introducing any additional photolithography step, we are able to control the final thickness of the substrate with an accuracy of  $\pm 10 \ \mu m$  in a 50  $\mu m$  thick substrate. In this work, we have shown P- and N-MOS devices on a flexible monocrystalline silicon substrate parting from standard 8 in. SOI wafers. We have chosen to characterize P-MOS devices in depth due to its scaled gate length (250 nm). It is to be noted that both N- and P-MOS devices were fabricated on the same wafer and transformed into flexible ones at the same time, showing the compatibility of our process with CMOS based electronics. Due to variations in threshold voltage between N- and P-MOS devices, we were not able to demonstrate CMOS circuitry. However, it can be seen that the transistor performance is kept almost unaltered when comparing flexible devices with bulk devices. The fabricated transistor feature the most advanced architecture nowadays used in industry as well as the most sophisticated set of materials for the creation of the high- $\kappa$ /metal-gate stack. Electrical characterization of the devices shows that the performance of the transistors is kept unaltered with the introduction of our process. With a maximum change of 7.6% in the saturation current and 5.1% change in threshold voltage of the fabricated devices under different stress conditions, we show that we can transform state of the art rigid CMOS circuitry into flexible ones without sacrificing the performance of the devices. The flexible devices have a final thickness of 50  $\mu$ m giving us the ability to bend the substrate to a minimum-bending radius of 1.5 cm. The fabricated devices show competitive electrical behavior (Table 1) and bendability relying solely on mature micro- and nanofabrication techniques. Finally, we believe our process sets a step forward toward very large integration of flexible high-performance circuitry that in the future may be used in ultramobile applications.

## CONCLUSION

We have reported a flexible (0.5 mm bending radius) nanoscale FinFET on silicon-on-insulator using a backetch based substrate thinning process (50  $\mu$ m silicon fabric). The process proves to be gentler than the traditional abrasive back grinding process and also does not introduce network of holes/trenches, typical signature of our previously demonstrated trench-protect-release-reuse process. Comprehensive electrical characterizations using various bending radii (both upward and downward direction) show no performance degradation (compared to the FinFETs on rigid-bulk-traditional SOI substrate). The study is a concrete step forward toward introduction of flexible high-performance electronics for the Internet of Things (IoT).

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. We acknowledge the support from KAUST OCRF Competitive Research Grant: CRG-1-2012-HUS-008 for this work.

#### **REFERENCES AND NOTES**

- Yong, X.; Yu-Chong, T.; Huang, A.; Chih-Ming, H. IC-Integrated Flexible Shear-Stress Sensor Skin. J. Microelectromech. Syst. 2003, 12, 740–747.

- Eun-Soo, H.; Jung-hoon, S.; Yong-Jun, K. A Polymer-Based Flexible Tactile Sensor for Both Normal and Shear Load Detections and Its Application for Robotics. J. Microelectromech. Syst. 2007, 16, 556–563.

- Rogers, J. A.; Bao, Z.; Baldwin, K.; Dodabalapur, A.; Crone, B.; Raju, V. R.; Kuck, V.; Katz, H.; Amundson, K.; Ewing, J.; *et al.* Paper-like Electronic Displays: Large-Area Rubber-Stamped Plastic Sheets of Electronics and Microencapsulated Electrophoretic Inks. *Proc. Natl. Acad. Sci. U.S.A.* 2001, *98*, 4835–4840.

- Baca, A. J.; Ahn, J.-H.; Sun, Y.; Meitl, M. A.; Menard, E.; Kim, H.-S.; Choi, W. M.; Kim, D.-H.; Huang, Y.; Rogers, J. A.

- VOL.8 NO.10 9850-9856 2014 A

Semiconductor Wires and Ribbons for High-Performance Flexible Electronics. *Angew. Chem., Int. Ed.* **2008**, *47*, 5524–5542.

- Forrest, S. R. The Path to Ubiquitous and Low-Cost Organic Electronic Appliances on Plastic. *Nature* 2004, 428, 911– 918.

- Sun, J.; Zhang, B.; Katz, H. E. Materials for Printable, Transparent, and Low-Voltage Transistors. *Adv. Funct. Mater.* 2011, *21*, 29–45.

- Kang, S. J.; Kocabas, C.; Ozel, T.; Shim, M.; Pimparkar, N.; Alam, M. A.; Rotkin, S. V.; Rogers, J. A. High-Performance Electronics Using Dense, Perfectly Aligned Arrays of Single-Walled Carbon Nanotubes. *Nat. Nanotechnol.* 2007, 2, 230–236.

- Lee, S.-K.; Kim, B. J.; Jang, H.; Yoon, S. C.; Lee, C.; Hong, B. H.; Rogers, J. A.; Cho, J. H.; Ahn, J.-H. Stretchable Graphene Transistors with Printed Dielectrics and Gate Electrodes. *Nano Lett.* 2011, *11*, 4642–4646.

- Moon, J.; Curtis, D.; Hu, M.; Wong, D.; Campbell, P.; Jernigan, G.; Tedesco, J.; VanMil, B.; Myers-Ward, R.; Eddy, C. Development toward Wafer-Scale Graphene RF Electronics. In 2010 Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), New Orleans, LA, January 11–13, 2010; IEEE: Piscataway, NJ, 2010; pp 1–3.

- Ahn, J.-H.; Kim, H.-S.; Lee, K. J.; Jeon, S.; Kang, S. J.; Sun, Y.; Nuzzo, R. G.; Rogers, J. A. Heterogeneous Three-Dimensional Electronics by Use of Printed Semiconductor Nanomaterials. *Science* 2006, *314*, 1754–1757.

- Yoon, J.; Baca, A. J.; Park, S.-I.; Elvikis, P.; Geddes, J. B.; Li, L.; Kim, R. H.; Xiao, J.; Wang, S.; Kim, T.-H.; Motala, M. J.; *et al.* Ultrathin Silicon Solar Microcells for Semitransparent, Mechanically Flexible and Microconcentrator Module Designs. *Nat. Mater.* **2008**, *7*, 907–915.

- Ko, H. C.; Stoykovich, M. P.; Song, J.; Malyarchuk, V.; Choi, W. M.; Yu, C.-J.; Geddes Iii, J. B.; Xiao, J.; Wang, S.; Huang, Y.; et al. A Hemispherical Electronic Eye Camera Based on Compressible Silicon Optoelectronics. *Nature* **2008**, 454, 748–753.

- Park, S.-I.; Xiong, Y.; Kim, R.-H.; Elvikis, P.; Meitl, M.; Kim, D.-H.; Wu, J.; Yoon, J.; Yu, C.-J.; Liu, Z.; *et al.* Printed Assemblies of Inorganic Light-Emitting Diodes for Deformable and Semitransparent Displays. *Science* **2009**, *325*, 977–981.

- Rogers, J. A.; Someya, T.; Huang, Y. Materials and Mechanics for Stretchable Electronics. *Science* 2010, 327, 1603–1607.

- Yoon, J.; Li, L.; Semichaevsky, A. V.; Ryu, J. H.; Johnson, H. T.; Nuzzo, R. G.; Rogers, J. A. Flexible Concentrator Photovoltaics Based on Microscale Silicon Solar Cells Embedded in Luminescent Waveguides. *Nat. Commun.* 2011, 2, 343.

- Rogers, J. A.; Lagally, M. G.; Nuzzo, R. G. Synthesis, Assembly and Applications of Semiconductor Nanomembranes. *Nature* 2011, 477, 45–53.

- Song, Y. M.; Xie, Y.; Malyarchuk, V.; Xiao, J.; Jung, I.; Choi, K.-J.; Liu, Z.; Park, H.; Lu, C.; Kim, R.-H.; *et al.* Digital Cameras with Designs Inspired by the Arthropod Eye. *Nature* **2013**, *497*, 95–99.

- Lee, S.-K.; Jang, H.; Hasan, M.; Koo, J. B.; Ahn, J.-H. Mechanically Flexible Thin Film Transistors and Logic Gates on Plastic Substrates by Use of Single-Crystal Silicon Wires from Bulk Wafers. *Appl. Phys. Lett.* **2010**, *96*, 173501– 173503.

- Saha, S.; Hilali, M. M.; Onyegam, E. U.; Sarkar, D.; Jawarani, D.; Rao, R. A.; Mathew, L.; Smith, R. S.; Xu, D.; Das, U. K.; *et al.* Single Heterojunction Solar Cells on Exfoliated Flexible <25μm Thick Mono-Crystalline Silicon Substrates. *Appl. Phys. Lett.* **2013**, *102*, 163904–163906.

- Bedell, S. W.; Bayram, C.; Fogel, K.; Lauro, P.; Kiser, J.; Ott, J.; Zhu, Y.; Sadana, D. Vertical Light-Emitting Diode Fabrication by Controlled Spalling. *Appl. Phys. Express.* **2013**, *6*, 112301–112303.

- Burghartz, J. N.; Appel, W.; Rempp, H. D.; Zimmermann, M. A New Fabrication and Assembly Process for Ultrathin Chips. *IEEE Trans. Elect. Dev.* 2009, *56*, 321–327.

- 22. Sanda, H.; McVittie, J.; Koto, M.; Yamagata, K.; Yonehara, T.; Nishi, Y. Fabrication and Characterization of CMOSFETs on Porous Silicon for Novel Device Layer Transfer. In *IEDM*

Technical Digest IEEE International Electron Devices Meeting, 2005, Washington, DC., December 5, 2005; IEEE: Piscataway, NJ, 2005; pp 679–682.

- Rojas, J. P.; Torres Sevilla, G. A.; Hussain, M. M. Can We Build a Truly High Performance Computer Which Is Flexible and Transparent? [Online]. *Sci. Rep.* 2013, *3*, No. 260910.1038/ srep02609.

- Torres Sevilla, G. A.; Rojas, J. P.; Fahad, H. M.; Hussain, A. M.; Ghanem, R.; Smith, C. E.; Hussain, M. M. Flexible and Transparent Silicon-On-Polymer Based Sub-20 nm Non-Planar 3D FinFET for Brain-Architecture Inspired Computation. *Adv. Mater.* 2014, *26*, 2794–2799.

- Torres Sevilla, G. A.; Rojas, J. P.; Ahmed, S.; Hussain, A.; Bin Inayat, S.; Hussain, M. M. Silicon Fabric for Multi-Functional Applications. In 2013 Transducers & Eurosensors XXVII: The 17th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS & EUROSENSORS XXVII), Barcelona, Spain, June 16–20, 2013; IEEE: Piscataway, NJ, 2013; pp 2636–2639.

- Rojas, J. P.; Torres Sevilla, G. A.; Ghoneim, M. T.; Inayat, S. B.; Ahmed, S. M.; Hussain, A. M.; Hussain, M. M. Transformational Silicon Electronics. ACS Nano 2014, 8, 1468–1474.

- Torres Sevilla, G. A.; Inayat, S. B.; Rojas, J. P.; Hussain, A. M.; Hussain, M. M. Flexible and Semi-Transparent Thermoelectric Energy Harvesters from Low Cost Bulk Silicon (100). Small 2013, 9, 3916–3921.

- 28. Schroder, D. K. Semiconductor Material and Device Characterization; Wiley-IEEE Press: Germany, 2006.

- 29. Wang, J. Stress Effects on MOSFETs. Ph.D., Arizona State University, Ann Arbor, MI, 2008.

- Shahrjerdi, D.; Bedell, S. W.; Khakifirooz, A.; Fogel, K.; Lauro, P.; Cheng, K.; Ott, J. A.; Gaynes, M.; Sadana, D. K. Advanced Flexible CMOS Integrated Circuits on Plastic Enabled by Controlled Spalling Technology. In *IEDM Technical Digest IEEE International Electron Devices Meeting, Washington, DC, December 10–13, 2012*; IEEE: Piscataway, NJ, 2012; pp 5.1.1–5.1.4.

- Kavalieros, J.; Doyle, B.; Datta, S.; Dewey, G.; Doczy, M.; Jin, B.; Lionberger, D.; Metz, M.; Rachmady, W.; Radosavljevic, M.; Shah, U.; Zelick, N.; Chau, R. Tri-Gate Transistor Architecture with High-k Gate Dielectrics, Metal Gates and Strain Engineering. In *Digest of Technical Papers*. 2006 Symposium on VLSI Technology, Honolulu, HI; IEEE: Piscataway, NJ, 2006; pp 50–51.

- Xia, Y.; Kalihari, V.; Frisbie, C. D.; Oh, N. K.; Rogers, J. A. Tetracene Air-gap Single-Crystal Field-Effect Transistors. *Appl. Phys. Lett.* 2007, *90*, 162106.

- Zhai, Y.; Mathew, L.; Rao, R.; Xu, D.; Banerjee, S. K. High-Performance Flexible Thin-Film Transistors Exfoliated from Bulk Wafer. *Nano Lett.* 2012, *12*, 5609–5615.

9856